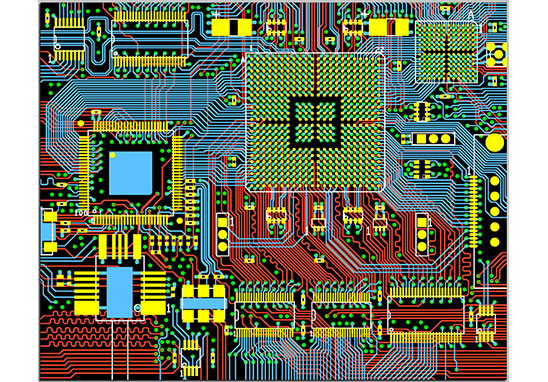

科學技術的高速發(fā)展就決定了所有企業(yè)都要有提升����,其中PCB依賴于科技��,自然也不得落后����,因而高頻PCB的布局也就成了大家設計PCB高頻板時候需要探討的關鍵點��。接下來深圳PCB設計公司-深圳宏力捷為大家介紹下高頻PCB設計布局的注意要點���。

高頻PCB設計布局注意要點

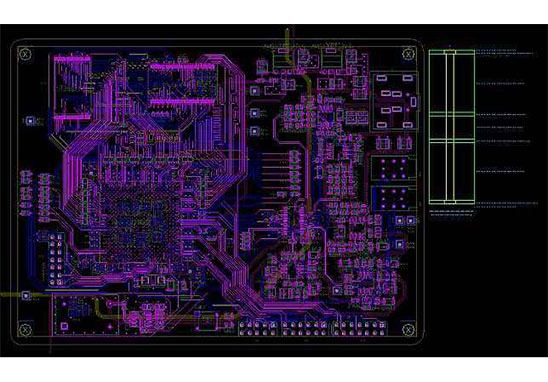

(1)高頻電路傾向于具有高集成度和高密度PCB設計布線����。使用多層板既是PCB設計布線所必需的����,也是減少干擾的有效手段�。

(2)高速電路裝置的引腳之間的引線彎曲越少越好���。高頻電路PCB設計布線的引線優(yōu)選為實線����,需要繞線�,并且可以以45°折疊線或圓弧折疊。為了滿足該要求��,可以減少高頻信號的外部傳輸和相互耦合���。

(3)高頻電路器件的引腳之間的引線越短越好�。

(4)高頻電路裝置的引腳之間的配線層之間的交替越少越好��。所謂“盡可能減少層間交叉”是指在組件連接過程中使用的過孔(Via)越少越好���,據(jù)估計�����,一個過孔可以帶來大約為0.5 pF的分布電容��。減少了過孔數(shù)量�����?�?梢源蟠筇岣咚俣?����。

(5)高頻電路PCB設計布線應注意信號線的平行線引入的“交叉干擾”���。如果無法避免并行分布���,則可以在并行信號線的背面布置大面積的“接地”,以大大減少干擾���。同一層中的平行走線幾乎是不可避免的,但是在相鄰的兩層中�����,走線的方向必須彼此垂直��。

(6)包圍特別重要的信號線或本地單元的接地措施�,即繪制所選對象的外輪廓��。使用此功能��,可以在所選的重要信號線上自動執(zhí)行所謂的“數(shù)據(jù)包”處理����。當然��,對于高速系統(tǒng)來說�,將此功能用于時鐘等組件的本地處理也是非常有益的。

(7)各種類型的信號走線不能形成環(huán)路����,并且接地線也不能形成電流環(huán)路。

(8)應在每個集成電路塊附近放置一個高頻去耦電容器����。

(9)將模擬接地線和數(shù)字接地線連接到公共接地線時,應使用高頻湍流鏈路�。在高頻湍流鏈的實際組裝中,經(jīng)常使用穿過中心孔的高頻鐵氧體磁珠��,并且在電路原理圖中通常沒有表示��,并且所得的網(wǎng)表不包括此類組件,PCB設計布線將忽略其存在���。響應于此現(xiàn)實��,它可以用作原理圖中的電感器����,并且在PCB組件庫中單獨定義組件封裝����,并在PCB設計布線之前將其手動移動到公共接地線的會聚點附近的合適位置。

(10)模擬電路和數(shù)字電路應分開布置���。獨立PCB設計布線后���,電源和地線應連接在一個點上,以避免相互干擾��。

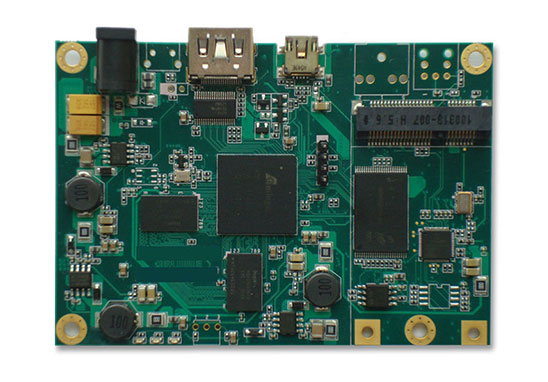

(11)在將DSP芯片外程序存儲器和數(shù)據(jù)存儲器連接到電源之前����,應添加濾波電容器并將其盡可能靠近芯片電源引腳放置���,以濾除電源噪聲����。另外,建議在DSP和片外程序存儲器以及數(shù)據(jù)存儲器周圍進行屏蔽�����,以減少外部干擾�����。

(12)芯片外程序存儲器和數(shù)據(jù)存儲器應盡可能靠近DSP芯片放置�����。同時����,布局應合理,以使數(shù)據(jù)線和地址線的長度基本相同����,尤其是當系統(tǒng)中有多個存儲器時,應考慮每個存儲器的時鐘線�。時鐘輸入距離相等,或者可以添加單獨的可編程時鐘驅(qū)動器芯片。對于DSP系統(tǒng)���,應選擇訪問速度與DSP相同的外部存儲器��,否則將無法充分利用DSP的高速處理能力�����。DSP指令周期為納秒�,因此DSP硬件系統(tǒng)中最常見的問題是高頻干擾���。因此����,在制作DSP硬件系統(tǒng)的印刷電路板(PCB)時�����,應特別注意地址線和數(shù)據(jù)線����。信號線的接線應正確合理。接線時��,請嘗試使高頻線短而粗����,并遠離易受干擾的信號線,例如模擬信號線����。當DSP周圍的電路更復雜時,建議將DSP及其時鐘電路����,復位電路,片外程序存儲器和數(shù)據(jù)存儲器組成一個最小的系統(tǒng)�,以減少干擾。

以上就是關于高頻PCB設計布局注意要點的介紹�����,深圳宏力捷電子是一家專業(yè)從事電子產(chǎn)品電路板設計(layout布線設計)的PCB設計公司���,主要承接多層�、高密度的PCB設計畫板及電路板設計打樣業(yè)務���。擁有平均超過10年工作經(jīng)驗的PCB設計團隊�,能熟練運用市場主流PCB設計軟件,專業(yè)高效溝通保證PCB設計進度��,助您早一步搶占市場先機���!

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料