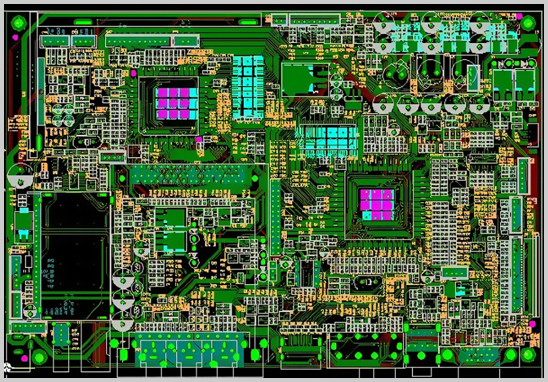

四層PCB廣泛應(yīng)用于復(fù)雜電子設(shè)備中�����,因其具有更高的信號完整性和更強的電磁兼容性�����,成為現(xiàn)代電子產(chǎn)品設(shè)計的主流選擇�。深圳宏力捷電子作為一家經(jīng)驗豐富的PCB設(shè)計公司����,深知四層PCB的設(shè)計和打樣過程具有一定的復(fù)雜性�。

1. 層疊設(shè)計的合理性

概念:四層PCB的層疊結(jié)構(gòu)通常由兩層信號層和兩層電源/接地層組成���。層疊設(shè)計對信號完整性和電磁兼容性至關(guān)重要�。

常見問題:不合理的層疊設(shè)計可能導(dǎo)致信號串?dāng)_��、阻抗不匹配以及輻射干擾等問題��。

解決方案:最佳實踐是將電源層和接地層放置在中間兩層�����,外層作為信號層����。這樣不僅有利于減小層間的寄生電感,還能有效屏蔽外部干擾����。特別是信號層應(yīng)避免長距離的平行走線,以減少信號串?dāng)_�。

2. 電源和地平面的完整性

概念:在四層PCB設(shè)計中,電源層和地層的完整性直接影響信號傳輸?shù)馁|(zhì)量和電路的穩(wěn)定性�。

常見問題:電源或接地層中存在不連續(xù)或切割的情況�����,會導(dǎo)致電源噪聲增加和信號的電壓波動��。

解決方案:在設(shè)計時應(yīng)確保電源層和地層的完整性���,避免不必要的切割。通過減少過孔數(shù)量��,確保電源和接地平面保持連續(xù)���。同時����,盡量在接地層上提供完整���、無切割的回流路徑����,以減少信號的電磁干擾��。

3. 阻抗匹配設(shè)計

概念:對于高速電路設(shè)計�����,信號的阻抗匹配是確保信號質(zhì)量的關(guān)鍵����。阻抗不匹配會導(dǎo)致信號反射,進而影響信號完整性��。

常見問題:在高速PCB中���,未能正確考慮阻抗匹配可能導(dǎo)致信號失真�����、數(shù)據(jù)丟失��,甚至設(shè)備無法正常工作�����。

解決方案:在設(shè)計階段��,首先需要計算并確保關(guān)鍵信號的走線寬度和層疊結(jié)構(gòu)符合阻抗要求�����。使用計算工具精確地設(shè)計阻抗匹配����,并嚴(yán)格按照生產(chǎn)廠商的參數(shù)進行設(shè)計,以確保最終產(chǎn)品符合設(shè)計規(guī)范����。

4. 過孔設(shè)計的合理性

概念:過孔是將信號從一個層傳輸?shù)搅硪粋€層的重要途徑,但其設(shè)計不當(dāng)會引發(fā)信號完整性問題�,特別是在四層板上。

常見問題:過多或不合理的過孔設(shè)計會引起信號反射和串?dāng)_�,同時增加信號的傳輸路徑,導(dǎo)致信號延遲和衰減�����。

解決方案:合理安排過孔的位置和數(shù)量�����,盡量減少不必要的過孔����。高速信號的走線應(yīng)盡量減少層間切換�����,避免信號延遲。同時使用盲孔或埋孔技術(shù)可以進一步優(yōu)化信號傳輸��。

5. 信號走線的長度匹配

概念:在高速數(shù)字電路中�,差分信號和時鐘信號的長度匹配非常重要,長度不一致會導(dǎo)致信號延遲和同步問題�。

常見問題:未能對差分信號進行精確的長度匹配,可能導(dǎo)致數(shù)據(jù)傳輸中的誤碼率增加�,甚至引發(fā)數(shù)據(jù)丟失。

解決方案:對于差分對信號����,應(yīng)嚴(yán)格控制兩條走線的長度,確保它們的長度差在允許的范圍內(nèi)�。可以使用蛇形走線的方式來平衡走線長度���。此外�����,盡量保持時鐘信號和其他高速信號的等長���,以確保信號同步����。

結(jié)論

四層PCB的設(shè)計與打樣是一項復(fù)雜且精密的工作����,每一個細(xì)節(jié)都可能影響到最終的產(chǎn)品質(zhì)量。深圳宏力捷電子憑借多年的PCB設(shè)計經(jīng)驗���,在四層PCB的打樣設(shè)計中有著豐富的技術(shù)積累��。通過關(guān)注層疊設(shè)計���、電源地平面完整性、阻抗匹配���、過孔設(shè)計和信號走線長度匹配等細(xì)節(jié)�����,我們確保每個設(shè)計都能滿足客戶的高標(biāo)準(zhǔn)要求�。在選擇PCB設(shè)計合作伙伴時��,宏力捷電子將是您的可靠之選,為您提供高效���、優(yōu)質(zhì)的四層PCB設(shè)計服務(wù)�����。

深圳宏力捷推薦服務(wù):PCB設(shè)計打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料